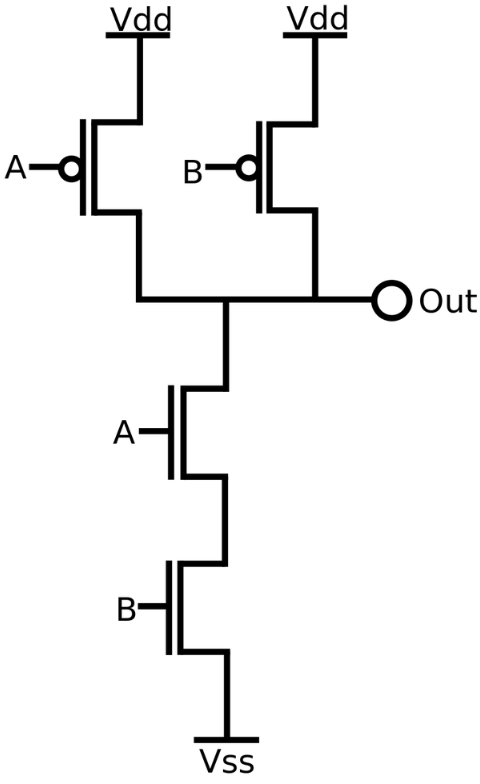

0. transmission gate(전달게이트) 설명손실 없는 신호 전달을 위해 PMOS와 NMOS를 병렬로 연결한 스위치와 같습니다.NMOS와 PMOS는 신호 전달 시에 문턱전압으로 인한 손실이 발생합니다.NMOS는 low 값 전달 시에는 손실이 없지만, VDD(high) 값 전달 시 문턱전압만큼 손실이 발생합니다.반대로 PMOS는 high 신호는 잘 통과하지만문턱전압만큼 손실합니다. PMOS와 NMOS를 병렬로 연결한다면 high 신호는 PMOS를 통해 손실 없이 전달되고 low 신호는 NMOS를 통해 손실 없이 전달됩니다. 트랜지스터를 2배로 사용해야 하지만 신호를 잘 전달하는 특성 때문에 쓰입니다.1. Schematic & Layout전달 게이트를 구성하는 2개의 MOSFET으로 이루어집니다.F..